# **Fundamental Characteristics of Thyristors**

#### Introduction

The thyristor family of semiconductors consists of several very useful devices. The most widely used of this family are silicon controlled rectifiers (SCRs), triacs, and diacs. There are many applications where these devices perform key functions and are real assets in meeting environmental, speed, and reliability specifications which their electro-mechanical counterparts cannot fulfill. Since they are different from their electro-mechanical counterparts in many ways, there are many characteristics, terms and parameters which must be understood. The purpose of this application note is to better acquaint users of SCRs, triacs, and diacs to the basic fundamentals of these thyristors.

## **Basic Operation of an SCR**

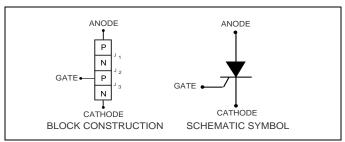

Simple block construction of an SCR is shown in Figure 14.1.

Figure 14.1 SCR Block Construction

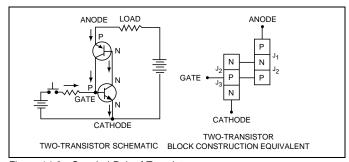

The operation of a PNPN device can best be visualized as a specially coupled pair of transistors as shown in Figure 14.2.

Figure 14.2 Coupled Pair of Transistors

The connections between the two transistors are such that regenerative action can occur when a proper gate signal is applied to the base of the NPN transistor. Normal leakage current is so low that the combined  $h_{FE}$  of the specially coupled two-transistor feedback amplifier is less than unity, thus keeping the circuit in an off-state condition. A momentary positive pulse applied to the gate will bias the NPN transistor into conduction which, in turn, biases the PNP transistor into conduction. The effective  $h_{FE}$  momentarily becomes greater than unity so that the specially coupled transistors saturate. Once saturated, current through the transistors is enough to keep the combined  $h_{FE}$  greater than unity. The circuit will remain "on" until it is "turned off" by reducing the anode-to-cathode current ( $I_{T}$ ) such that the combined  $h_{FE}$  is

less than unity and regeneration ceases; this threshold anode current is the holding current of the SCR.

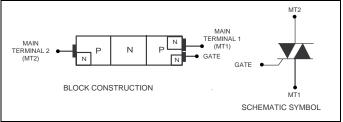

### **Basic Operation of a Triac**

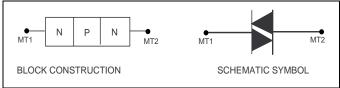

Simple block construction of a triac is shown in Figure 14.3. Its primary function is to control power bilaterally in an AC circuit.

Figure 14.3 Triac Block Construction

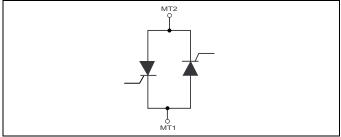

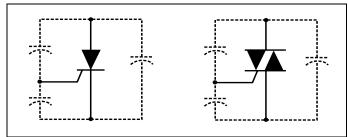

Operation of a triac can be related to two SCRs connected in parallel in opposite directions as shown in Figure 14.4.

Although the gates are shown separately for each SCR in Figure 14.4, a triac has a single gate and can be triggered by either polarity.

Figure 14.4 Connected SCRs

Since a triac operates in both directions, it behaves essentially the same in either direction as an SCR would behave in the forward direction (blocking or operating)

## **Basic Operation of a Diac**

The construction of a diac is similar to an open base "NPN" transistor. A simple block diagram is shown in Figure 14.5.

Figure 14.5 Diac Block Construction

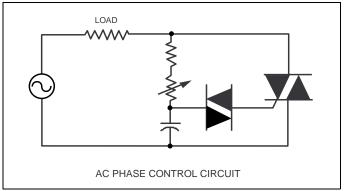

The bidirectional transistor-like structure exhibits a high-impedance blocking state up to a voltage breakover point ( $V_{BO}$ ) above which the device enters a negative-resistance region. These basic diac characteristics produce a bidirectional pulsing oscillator in a resistor-capacitor AC circuit. Since the diac is a bidirec-

tional device, it makes a good economical trigger for firing triacs in phase control circuits like light dimmers, motor speed controls, etc. Figure 14.6 is a simplified AC circuit using a diac and a triac in a phase control application.

Figure 14.6 AC Phase Control Circuit

#### **Geometric Construction of an SCR**

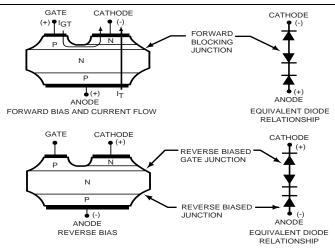

Figure 14.7 shows cross-sectional views of an SCR chip. Also included are illustrations of current flow and junction biasing in both the blocking and triggering modes.

Figure 14.7 Cross-Sectional View of SCR Chip

## **Geometric Construction of a TRIAC**

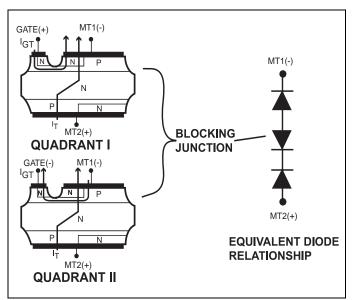

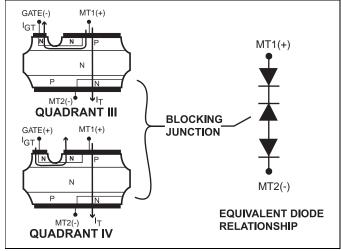

Figures 14.8 and 14.9 give simplified cross-sectional views of a triac chip. Illustrations are shown in various gating quadrants and blocking modes.

Figure 14.8 Simplified Cross-Sectional of SCR Chip (Quadrants I and II)

Figure 14.9 Simplified Cross-Sectional of SCR Chip (Quadrants III and II)

#### **Geometric Construction of a Diac**

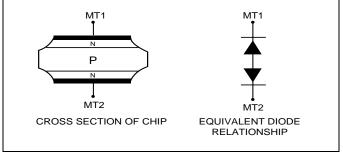

Figure 14.10 gives a cross-sectional view of a diac chip.

Figure 14.10 Cross-Sectional View of Diac Chip

## **Fundamental Characteristics of Thyristors**

## **Electrical Characteristic Curves of Thyristors**

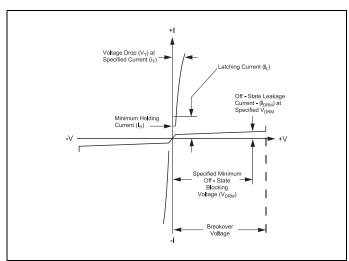

## Voltage Drop (V<sub>T</sub>) at Latching Current (I) Off - State Leakage Reverse Leakage Current - (I<sub>DRM</sub>) at Specified V<sub>DRM</sub> Specified V<sub>RR</sub> Minimum Holding Current (IH) Specified Minimum Specified Minimum Off - State rse Blockina Blocking Voltage (V<sub>RRM</sub>) Forward Voltage Voltage

Figure 14.11 V-I Characteristics of SCR Device

Figure 14.12 V-I Characteristics of Triac Device

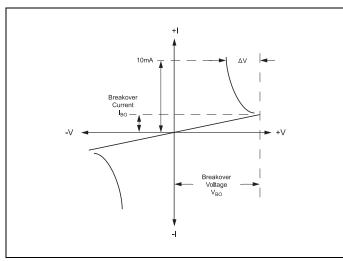

Figure 14.13 V-I Characteristics of Bilateral Trigger Diac

## **Methods of Switching on Thyristors**

There are three general ways to switch thyristors to on-state condition:

- Application of Gate Signal

- Static dv/dt Turn-On

- Voltage Breakover Turn-On

Listed below is a brief description of each method.

#### **Application Of Gate Signal**

Must exceed  $I_{GT}$  and  $V_{GT}$  requirements of thyristor being used. For an SCR (unilateral device), this signal must be positive with respect to the cathode polarity. A triac (bilateral device) can be turned on with gate signal of either polarity; however, different polarities have different requirements of  $I_{GT}$  and  $V_{GT}$  which must be satisfied. Since a diac does not have a gate, this method of turn-on is not applicable to diacs; in fact, the single major application of diacs is to switch-on triacs.

#### Static dv/dt Turn-On

Comes from a fast rising voltage applied across the anode and cathode terminals of an SCR or the main terminals of a triac. Due to the nature of thyristor construction, a small junction capacitor is formed across each PN junction. Figure 14.14 shows how typical internal capacitors are linked in gated thyristors. When voltage is impressed suddenly across a PN junction, a charging current will flow which is equal to:

$$i = C \left(\frac{dv}{dt}\right)$$

When  $C\left(\frac{dv}{dt}\right)$  becomes greater or equal to thyristor IGT, the thy-

ristor switches on. Normally, this type of turn on does not damage or hurt the device providing the surge current is limited.

Figure 14.14 Internal Capacitors Linked in Gated Thyristors

Generally, thyristor application circuits are designed with static dv/dt snubber networks if fast rising voltages are anticipated.

#### **Voltage Breakover Turn-On**

Is the method used to switch on diacs. However, exceeding voltage breakover of SCRs and triacs is definitely not recommended as a turn-on method.

In the case of SCRs and triacs, the leakage current increases until it exceeds the gate current required to turn-on these gated thyristors in a small localized point. When turn-on occurs by this method, there is localized heating in a small area which may melt the silicon or damage the device if di/dt of the increasing current is not sufficiently limited.

Diacs used in typical phase control circuits are basically protected against excessive current at breakover as long as the firing capacitor is not excessively large. When diacs are used in a zener function, current limiting is necessary.

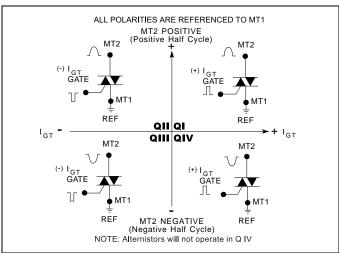

## **Triac Gating Modes Of Operation**

Triacs can be gated in four basic gating modes as shown in Figure 14.15.

The most common quadrants for triac gating-on are Quadrants I and III, where the gate supply is synchronized (gate positive, MT2 positive; or gate negative, MT2 negative) with the main terminal supply. Gate sensitivity of triacs is most optimum in Quadrants I and III due to the inherent thyristor chip construction. If, however, Quadrants I and III operation cannot be used, the next best operating modes are Quadrants II and III where the gate has a negative polarity supply with an AC main terminal supply. Typically, Quadrant II is approximately equal in gate sensitivity to Quadrant I; however, latching current sensitivity in Quadrant II is lowest. Therefore, it is difficult for triacs to latch on in quadrant II when the main terminal current supply is very low in value.

Quadrant IV has the lowest gate sensitivity of all four operating quadrants. Considerations should be given in gating circuit design when Quadrants I and IV are used in actual application.

Figure 14.15 Gating Modes

#### **General Terminology**

The following listings represent the most widely used thyristor terms, symbols and definitions. These terms, symbols and definitions conform to existing EIA-JEDEC standards.

Breakover Point - Any point on the principal voltage-current characteristic for which the differential resistance is zero and where the principal voltage reaches a maximum value.

**Principal Current** – A generic term for the current through the collector junction. Note: It is the current through main terminal 1 and main terminal 2 of a triac or anode and cathode of an SCR.

Principal Voltage - The voltage between the main terminals.

- (1) In the case of reverse blocking thyristors, the principal voltage is called positive when the anode potential is higher than the cathode potential, and called negative when the anode potential is lower than the cathode potential.

- (2) For bidirectional thyristors, the principal voltage is called positive when the potential of main terminal 2 is higher than the potential of main terminal 1.

Off-State - The condition of the thyristor corresponding to the high-resistance, low-current portion of the principal voltage-current characteristic between the origin and the breakover point(s) in the switching quadrant(s).

On-State - The condition of the thyristor corresponding to the low-resistance, low-voltage portion of the principal voltage-current characteristic in the switching quadrant(s).

#### Specific Terminology

Average Gate Power Dissipation  $[P_{G(AV)}]$  – The value of gate power which may be dissipated between the gate and main terminal 1 (or cathode) averaged over a full cycle.

Breakover Current (I<sub>BO</sub>) – The principal current at the breakover point.

Breakover Voltage (V<sub>BO</sub>) – The principal voltage at the breakover point.

Circuit-Commutated Turn-Off Time (tq) - The time interval between the instant when the principal current has decreased to zero after external switching of the principal voltage circuit, and the instant when the thyristor is capable of supporting a specified principal voltage without turning on.

Critical Rate-of-Rise of Commutation Voltage of a Triac (Commutating dv/dt) - The minimum value of the rate-of-rise of principal voltage which will cause switching from the off-state to the on-state immediately following on-state current conduction in the opposite quadrant.

Critical Rate-of-Rise of Off-State Voltage (Critical or Static dv/dt) - The minimum value of the rate-of-rise of principal voltage which will cause switching from the off-state to the onstate.

#### Critical Rate-of-Rise of On-State Current (di/dt)

The maximum value of the rate-of-rise of on-state current which a thyristor can withstand without deleterious effect.

Gate-Controlled Turn-On Time (t<sub>ot</sub>) – The time interval between a specified point at the beginning of the gate pulse and the instant when the principal voltage (current) has dropped (risen) to a specified low (high) value during switching of a thyristor from off-state to the on-state by a gate pulse.

Gate Trigger Current (I<sub>GT</sub>) – The minimum gate current required to maintain the thyristor in the on-state.

Gate Trigger Voltage (V<sub>GT</sub>) - The gate voltage required to produce the gate trigger current.

Holding Current (IH) - The minimum principal current required to maintain the thyristor in the on-state.

Latching Current (I) - The minimum principal current required to maintain the thyristor in the on-state immediately after switching from the off-state to the on-state has occurred and the triggering signal has been removed.

On-State Current (I<sub>T</sub>) - The principal current when the thyristor is in the on state.

On-State Voltage (V<sub>T</sub>) - The principal voltage when the thyristor is in the on-state.

## **Fundamental Characteristics of Thyristors**

## **Specific Terminology (continued)**

**Peak Gate Power Dissipation (P\_{GM})** – The maximum power which may be dissipated between the gate and main terminal 1 (or cathode) for a specified time duration.

Repetitive Peak Off-State Current (I<sub>DRM</sub>) – The maximum instantaneous value of the off-state current that results from the application of repetitive peak off-state voltage.

Repetitive Peak Off-State Voltage (V<sub>DRM</sub>) – The maximum instantaneous value of the off-state voltage which occurs across a thyristor, including all repetitive transient voltages, but excluding all non-repetitive transient voltages.

Repetitive Peak Reverse Current of an SCR (I<sub>RRM</sub>) – The maximum instantaneous value of the reverse current that results from the application of repetitive peak reverse voltage.

Repetitive Peak Reverse Voltage of an SCR (V<sub>RRM</sub>) – The maximum instantaneous value of the reverse voltage which occurs across the thyristor, including all repetitive transient voltages, but excluding all non-repetitive transient voltages.

Surge (Non-Repetitive) On-State Current (I<sub>TSM</sub>) – An onstate current of short-time duration and specified waveshape.

Thermal Resistance, Junction to Ambient ( $R_{\theta JA}$ ) – The temperature difference between the thyristor junction and ambient divided by the power dissipation causing the temperature difference under conditions of thermal equilibrium.

Note: Ambient is defined as the point where temperature does not change as the result of dissipation.

Thermal Resistance, Junction to Case ( $R_{\theta JC}$ ) – The temperature difference between the thyristor junction and the thyristor case divided by the power dissipation causing the temperature difference under conditions of thermal equilibrium.

# **Notes**